# **Tektronix**<sup>®</sup>

# Bit Error Rate Tester

BSX Series BERTScope<sup>®</sup> Datasheet

The BERTScope BSX-series Bit Error Rate Tester introduces a receiver test platform capable of supporting emerging Gen4 standards and beyond. With the addition of powerful data processing and internal Tx equalization, the BERTScope supports protocol-based handshaking and synchronization with your device under test (DUT), including interactive link training at data rates up to 32 Gb/s. The BSX-series shortens the time to debug physical layer and link training issues, and provides the quickest path to compliance for a broad range of standards.

#### Notice to EU customers

This product is not updated to comply with the RoHS 2 Directive 2011/65/ EU and will not be shipped to the EU. Customers may be able to purchase products from inventory that were placed on the EU market prior to July 22, 2017 until supplies are depleted. Tektronix is committed to helping you with your solution needs. Please contact your local sales representative for further assistance or to determine if alternative product(s) are available. Tektronix will continue service to the end of worldwide support life.

#### Key performance specifications

- Pattern Generation and Error Analysis up to 32 Gb/s

- Optional built-in 4-tap Tx equalization with support for interactive link training

- Protocol-oriented and bit-oriented multi-chain pattern sequencing with enhanced pattern/sequence editor

- User-defined detector pattern matching with stimulus-response feedback

- Patented Error Location Analysis<sup>™</sup> goes beyond BER measurement to provide insight into the sources of errors through analysis of correlations and deterministic error patterns

- Optional Forward Error Correction analysis provides for simulation of post-FEC error rate based upon measured error location patterns

- Integrated Eye Diagram Analysis with BER Correlation including Mask Testing, Jitter Peak, BER Contour

- Optional Jitter Map Comprehensive Jitter Decomposition with Long Pattern (i.e. PRBS-31) Jitter

#### **Key features**

- Provides a single solution for Receiver stress testing, debug and compliance

- Test Gen3 and Gen4 standards including PCIe, SAS, and USB3.1 and proprietary standards

- DUT handshaking capability above16 Gb/s supporting RX test requirements for loopback initiation and adaptive link training for key standards such as PCIe

- Protocol-aware pattern generation and error detection supports flexible stimulus response programmability and debugging of handshaking issues.

- Forward error correction (FEC) emulation option supports measurement of BER both before and after error correction for commonly used Reed-Solomon FEC codes.

- Calibration and test automation software available for key standards

#### Applications

- Design verification including signal integrity, jitter, and timing analysis

- Design characterization for high-speed, sophisticated designs

- Design/Verification of high-speed I/O components and systems including DUT handshaking

- Signal integrity analysis mask testing, jitter peak, BER contour, jitter map, and forward error correction emulation

# Intelligent memory sequencing

With both Bit Oriented and Protocol Aware memory sequencing modes available, and the ability to advance the sequencer based on a userdefined detector pattern match, the BSX series allows the user to create their own protocol-based patterns and handshaking sequences.

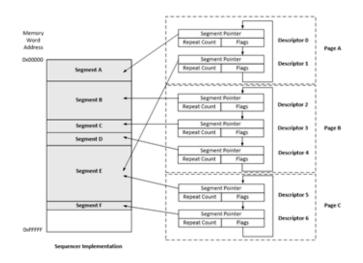

#### Pattern memory sequencer

The BSX-series memory sequencer implements flexible indirect access to pattern memory. The pattern memory can support two levels of loop nesting with up to 1 million iterations per loop. To further simplify programming and increase memory efficiency, individual pattern segments can be any size greater than 128 bits. Advancement of the memory sequence can be controlled by software control, external signal, or detector pattern match providing the user with multiple means for controlling handshaking with test devices.

#### Memory sequencer modes

To provide the user with more flexibility and simplicity in creating and detecting patterns and sequences, two distinct sequencer modes are offered, with both supporting the looping and sequence advance features described above:

Bit Oriented Sequencer mode. In bit-oriented mode, bits are sent unaltered from pattern memory to the Generator output with no protocol processing applied. This is equivalent to traditional BERT memory pattern operation.

- Protocol Aware Sequencer mode. In protocol-aware mode, pattern memory words are treated as protocol blocks or groups of symbols, instead of bits. Words are fetched from memory and processed according to the selected protocol or encoding. Depending upon the specific protocol requirements, protocol-oriented mode processing may include:

- Packaging of symbols into protocol blocks

- Symbol encoding

- Data scrambling

- DC balancing

This allows the user to input memory data in a "natural" format. Note that transition between sequencer states can be made without regard to data "stitching" problems since the sequencer maintains scrambling/ DC balancing states.

#### **Detector pattern matching**

The BSX-series supports optional user-defined Detector pattern matching which can be used to advance the Generator sequencer state. This capability allows flexible stimulus/response programmability to support debugging and proprietary protocols. As with the memory sequencer, the pattern matching supports two modes:

- Bit Oriented matching mode. Bit-oriented mode includes four generalpurpose Detector pattern matchers capable of finding any arbitrary pattern up to 128 bits in length in the incoming data stream, with bit masking available. A match can cause the sequencer to advance to the next state.

- Protocol Aware matching mode. Protocol-aware mode includes sixteen Detector pattern match elements for protocol-based pattern matching. For PCIe Gen3/4 and USB 3.1 Gen2, the Detector can match the entire decoded block payload, with bit/byte masking. For 8b/10b encoding, the detector can match up to 16, 8-bit symbols after block/symbol decoding with masking.

#### Protocol block/symbol filtering

Supported protocols have clock compensation (skip) and block/symbol filtering implanted, as is often required for independent clock operation. A protocol-filtering toggle in the Detector switches between raw bitstream and filtered bitstream for BER measurement.

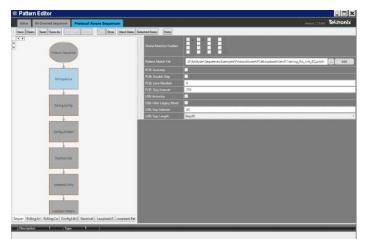

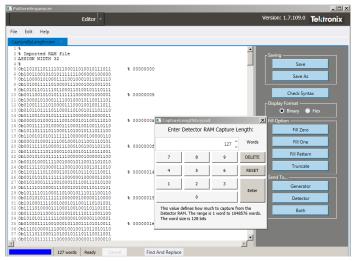

#### Pattern Sequencer editor

The BSX-series introduces a new pattern editor capable of supporting the bit-oriented and protocol-aware pattern as well as pattern sequence creation.

|                      |              | e Segment Fil              |               |     |      |     |            |     |      |    |        |    |      |      |      |      |      |      |  |  | Saving  |  |

|----------------------|--------------|----------------------------|---------------|-----|------|-----|------------|-----|------|----|--------|----|------|------|------|------|------|------|--|--|---------|--|

| loooding<br>Nouk Tys |              | Egun 3                     | ra Bieck 🔹    | Add | losk | ) + | . Pasitier |     | 6    | ¥. | (euto) |    |      |      |      |      |      |      |  |  | Save An |  |

|                      | Appeal       |                            | ure .         | (9) | (1)  | (2) | (0) (4     | 0.0 | 1.4  |    | 1 10   | 19 | [20] | (15) | (12) | (11) | (14) | [28] |  |  | Sent In |  |

|                      | 1:           | Standard Ski<br>Dete Elock | 2 Ordered Set |     |      |     | AA AJ      |     |      |    |        |    |      |      |      |      | 00   |      |  |  |         |  |

|                      | 64 .         | Data filock                |               |     |      |     | 00 00      |     |      |    |        |    |      |      | 00   | 00   | 53   |      |  |  |         |  |

| -                    | 54 -<br>51 - | Deta Block                 |               |     |      |     | 00 00      |     |      |    |        |    |      |      |      |      | 00   |      |  |  |         |  |

|                      | 64 1         | Data Block                 |               | 00  | 20   | 00  | 00 54      | 0 0 | 0 00 | 60 | 00     | 02 | 20   | 02   | 00   | -00  | 52   | 02   |  |  |         |  |

|                      |              |                            |               |     |      |     |            |     |      |    |        |    |      |      |      |      |      |      |  |  |         |  |

|                      |              |                            |               |     |      |     |            |     |      |    |        |    |      |      |      |      |      |      |  |  |         |  |

Sequence editor

In Protocol Aware Sequencer mode, the editor translates the symbolic protocol messages to protocol-specific blocks of data (without any transformation) in the generator pattern memory. These blocks are then processed by the protocol-specific memory sequencer. This simplifies the generation of complex protocol data streams.

Sequencer

# Linking domains

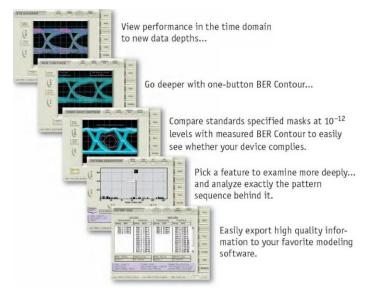

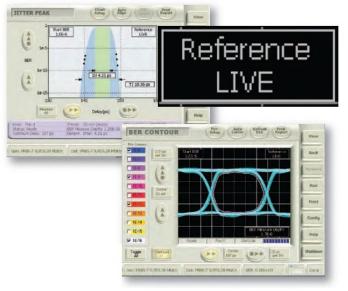

Eye diagrams have always provided an easy and intuitive view of digital performance. It has been harder to tie this directly with BER performance, as the instruments that provide views of each have been architected in fundamentally different ways. Eye diagrams have been composed of shallow amounts of data that have not easily uncovered rarer events. BERTs have counted every bit and so have provided measurements based on vastly deeper data sets, but have lacked the intuitive presentation of information to aid troubleshooting.

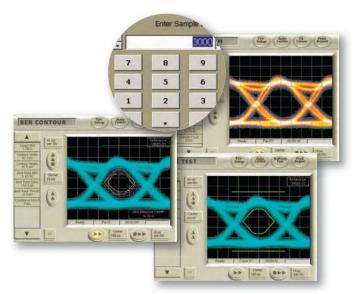

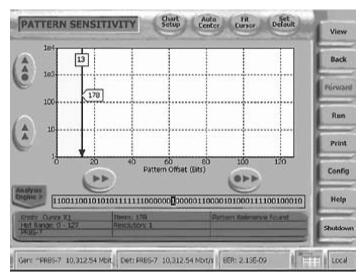

The BERTScope removes this gap allowing you to quickly and easily view an eye diagram based on at least two orders of magnitude more data than conventional eyes. Seeing a feature that looks out of the ordinary, you are able to place cursors on the item of interest and by simply moving the sampling point of the BERT, use the powerful error analysis capabilities to gain more insight into the feature of interest. For example, check for pattern sensitivity of the latest rising edges. Alternatively, use one-button measurement of BER Contour to see whether performance issues are bounded or likely to cause critical failures in the field. In each case, information is readily available to enhance modeling or aid troubleshooting, and is available for patterns up to 2<sup>31</sup> - 1 PRBS.

# Data rich eye diagrams

As shown previously, there is an impressive difference in data depth between conventional eye diagrams and those taken with a BERTScope. So what does that mean? It means that you see more of what is really going on - more of the world of low-probability events that is present every time you run a long pattern through a dispersive system of any kind, have random noise or random jitter from a VCO - a world that is waiting to catch you out when your design is deployed. Adding to this the deeper knowledge that comes from the one-button measurements of BER Contour, Jitter Peak, and Q-factor, and you can be confident that you are seeing the complete picture.

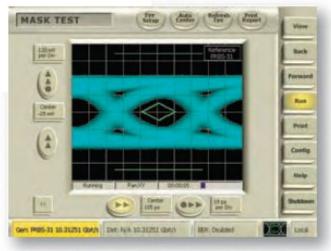

# Deep mask testing

With the ability to vary sample depth, it is very easy to move between deep measurements which give a more accurate view of the real system performance, and shallow measurements that match those of a sampling oscilloscope. The measurements shown below are from the eye diagram of an optical transmitter. With the BERTScope sample depth set to only 3000 waveforms, the BERTScope generates the diagram shown in the middle in only 1 second. The measured mask margin of 20% exactly correlates to the same measurement made on a sampling oscilloscope. The lower diagram shows the eye produced by the same device, using Compliance Contour measured at a BER of 1×10<sup>-6</sup>. Here the mask margin is reduced to 17%.

The depth advantage gained for eye diagrams is at least 10 times greater for mask testing. Unlike pseudo-mask testing offered by some BERTs, a BERTScope mask test samples every point on the perimeter of an industrystandard mask, including the regions above and below the eye. Not only that, but each point is tested to a depth unseen before. This means that even for a test lasting a few seconds using a mask from the library of standard masks or from a mask you have created yourself, you can be sure that your device has no lurking problems.

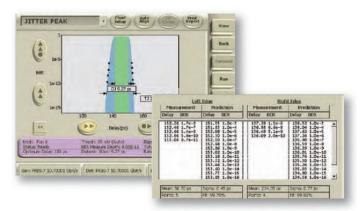

# Accurate jitter testing to industry standards

Testing with long or short patterns, the most accurate jitter measurement is likely to come from the methodology that uses little or no extrapolation to get its result. With the BERTScope, you can quickly measure to levels of  $1 \times 10^{-9}$  ( $1 \times 10$ -10 at high data rates), or wait for the instrument to measure  $1 \times 10^{-12}$  directly. Either way, the BERTScope's one-button measurements are compliant to the MJSQ jitter methodology, and because the underlying delay control is the best available on any BERT you can be sure that the measurements are accurate. Use the built-in calculations for Total Jitter (TJ), Random Jitter (RJ), and Deterministic Jitter (DJ), or easily export the data and use your own favorite jitter model.

The BSX-series low intrinsic RJ supports serving of 802.3ba's simultaneous VECP (Vertical Eye Closure Penalty) and J2/J9 calibration with valuable margin required to fully characterize 100G Ethernet silicon.

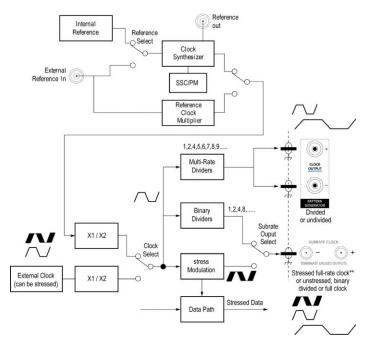

# **Flexible clocking**

The generator clock path features in the BERTScope provides the test flexibility needed for emerging real-world devices. Whether computer cards or disk drives, it is often necessary to be able to provide a sub-rate system clock, such as 100 MHz for PCI Express<sup>®</sup> (PCIe). To get the target card running may require a differential clock signal with a particular amplitude and offset; this is easily accomplished with the BERTScope architecture, with many flexible divide ratios available.

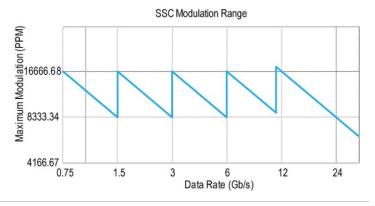

Spread Spectrum Clocking (SSC) is commonly used in electrical serial data systems to reduce EMI energy by dispersing the power spectrum. Adjustable modulation amplitude, frequency, and a choice of triangle or sine modulation wave shape allow testing receivers to any compliance standard which utilize SSC. An additional modulator and source allows users to stress the clock with high-amplitude, low-frequency Sinusoidal Jitter (SJ) at frequencies up to 4 MHz.

# Programmable reference clock multiplier

To further add clocking flexibility, the BSX series provides a general purpose reference clock multiplier that allows the user to specify an integer clock multiplication ratio for an input reference clock frequency range of 10 MHz to 200 MHz. The clock output frequency is bounded by the frequency range of the clock synthesizer, which is 1 GHz to 16 GHz in the case of BSX series. Predefined multiplication ratios are included for many common standards.

# Working with closed eyes

With the need to push ever-increasing data rates through electrical channels, the frequency-dependent losses often result in eye closure at the receiver end. Engineers use equalization to compensate for these losses and "open the eyes" in the real system. Tektronix offers powerful tools that allow designers to characterize and test compliance of receiver and transmitter components used in these systems.

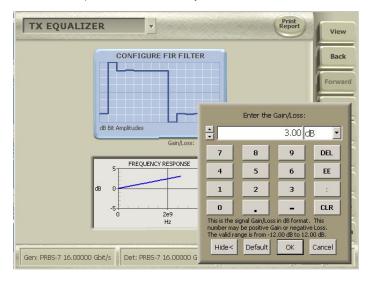

In keeping with the BERTScope philosophy, the graphical user interface presents the control functionality in a logical, easy-to-follow format. A time domain representation of the response shows the effects of tap weight settings. The frequency domain Bode plot shows how the filter will compensate for the channel losses.

For receiver testing, the BSX series included built-in 4-tap pre-emphasis/ de-emphasis capable of operation to the maximum data rate of the instrument, or 32 Gb/s in the case of the BSX320 model. Furthermore, fast control of output equalization supports link training response time requirements of the most stringent standards.

# PatternVu

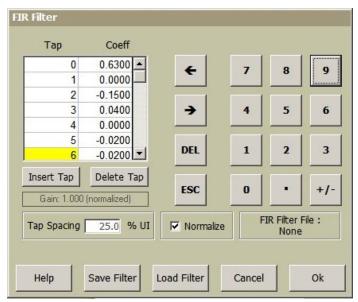

The PatternVu option includes a software-implemented FIR filter which can be inserted before the eye pattern display. In systems employing receiver equalization, this allows you to view the eye diagram and perform physical measurements on the eye as the receiver's detector would see it, after the effect of the equalizer. Equalizers with up to 32 taps can be implemented, and the user can select the tap resolution per UI.

PatternVu

PatternVu also includes CleanEye, a pattern-locked averaging system which removes the nondeterministic jitter components from the eye. This allows you to clearly see pattern-dependent effects such as ISI (Inter-Symbol Interference) which are normally obscured by the presence of high amounts of random jitter.

Single Value Waveform export is a component in the PatternVu option. This allows you to capture a pattern-locked waveform showing single bits, similar to a single-shot capture in a real-time oscilloscope. Once captured, the waveform can be exported in a variety of formats for further analysis in an external program.

# Add clock recovery

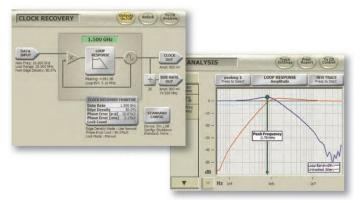

The Tektronix CR125A, CR175A, and CR286A add levels of flexibility in compliant clock recovery. Most standards requiring jitter measurement specify the use of clock recovery, and exactly which loop bandwidth must be used. Using a different or unknown loop bandwidth will almost certainly give you the wrong jitter measurement. The clock recovery instrument enables easy and accurate measurements to be made to all of the common standards.

The intuitive user interface provides easy control of all operating parameters. A unique Loop Response view shows the loop characteristics – actually measured, not just the settings value.

The usefulness of the BERTScope CR is not just confined to BERTScope measurements. Use them stand-alone in the lab with your sampling oscilloscopes, or with existing BERT equipment. Compliant measurements are available to you by pairing either of these versatile instruments with your existing investments.

In addition, lock status and measured parameters such as pattern edge density and phase error are available on both the local built-in display and the BERTScope user interface for real-time views of input signal characteristics and CR performance.

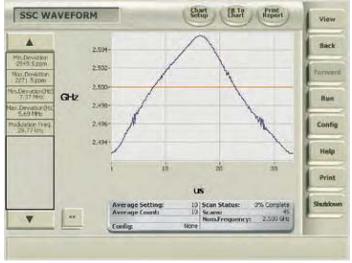

# **Display and measure SSC modulation**

Spread Spectrum Clocking (SSC) is used by many of the latest serial busses including SATA, PCI Express, and SAS to reduce EMI issues in new board and system designs. The Tektronix CR Family provides spread spectrum clock recovery together with the display and measurement of the SSC modulation waveform. Automated measurements include minimum and maximum frequency deviation (in ppm or ps), modulation rate of change (dF/dT), and modulation frequency. Also included are display of the nominal data frequency and easy-to-use vertical and horizontal cursors.

SSC waveform measurement

# Add jitter analysis

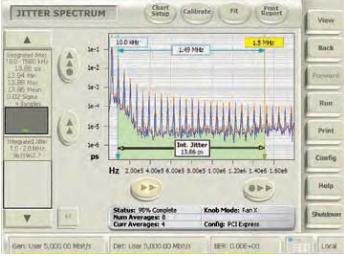

Combine a Tektronix CR125A, CR175A, or CR286A with Option 12GJ, 17GJ, and 28GJ respectively and your sampling oscilloscope or BERTScope for variable clock recovery from 1.2 to 11.2 Gb/s, Duty Cycle Distortion (DCD) measurement, and real-time jitter spectral analysis. Display jitter spectral components from 200 Hz to 90 MHz with cursor measurements of jitter and frequency. Measure band-limited integrated jitter with user-settable frequency-gated measurements (preset band limits and integrated jitter measurement for PCI Express 2.0 jitter spectrum in this example).

Jitter spectrum measurement

# Taking stress out of receiver testing

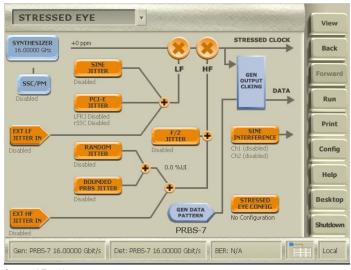

As networks have changed, so have the challenges of testing receivers. While tests such as BER and receiver sensitivity are still important, receiver jitter tolerance has evolved to be more real-world for jitter-limited systems such as 10 Gb/s data over back planes and new high-speed buses. Stressed Eye testing is becoming increasingly common as a compliance measurement in many standards. In addition, engineers are using it to explore the limits of their receiver performance to check margins in design and manufacturing. Creating the stress recipe for receiver testing to a complicated standard such as PCle 2.0 used to require "racking and stacking" several instruments, then spending hours calibrating the setup. With BERTScope, an easy-to-understand graphical view gives you control of all of the calibrated stress sources you need – inside the same instrument. Eliminating the need for external cabling, mixers, couplers, modulators, etc. simplifies stress calibration.

Stressed Eye view

# Flexible stress impairments

The BERTScope has high-quality, calibrated sources of stress built-in, including RJ, SJ, BUJ, and SI.

ISI is also a common ingredient in many standards. The BSA12500ISI differential ISI board provides a wide variety of path lengths, free from switching suck-outs and anomalies.

|          | Random Jitter                  |

|----------|--------------------------------|

| X3 HX3   | Sinusoidal Jitter              |

|          | Bounded<br>Uncorrelated Jitter |

| Twt twt  | Sinusoidal<br>Interference     |

| ХХ       | F/2 Sub-Rate<br>Clock Jitter   |

| $\times$ | Inter-Symbol<br>Interference   |

Flexible stress impairments

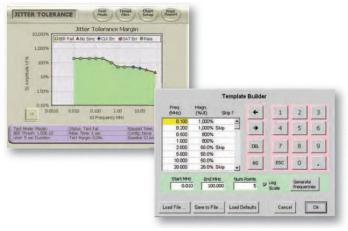

Many standards call for SJ to be stepped through a template with different SJ amplitudes at particular modulation frequencies. This is easy with the built-in Jitter Tolerance function which automatically steps through a template that you designed, or one of the many standard templates in the library.

Built-in jitter tolerance function

# **BERTScope pattern generators**

The BERTScope pattern generators provide a full range of PRBS patterns, common standards-based patterns, and user-defined patterns.

Option STR provides full integrated, calibrated stress generation which is an easy-to-use alternative to a rack full of manually calibrated instruments needed to provide a stressed pattern. Uses include receiver testing of devices with internal BER measurement ability such as DisplayPort, or adding stress capability to legacy BERT instruments.

XFI compliant electrical stressed eye

Stressed eye option

# **Pattern capture**

There are several methods for dealing with unknown incoming data. In addition to Live Data Analysis discussed above, a useful standard feature on all BERTScope analyzers is pattern capture. This allows the user to specify the length of a repeating pattern and then allow the analyzer to grab the specified incoming data using the detector's 512 Mb RAM memory. This can then be used as the new detector reference pattern, or edited and saved for later use.

Pattern capture

#### Pattern generator stressed eye

The pattern generator stressed eye function provides the following features:

- Flexible, integrated stressed eye impairment addition to the internal or an external clock

- Easy setup, with complexity hidden from the user with no loss of flexibility

- Verify compliance to multiple standards using the BERTScope and external ISI filters. Standards such as:

- OIF CEI

- 6 Gb SATA

- PCI Express

- XFI

0

- USB 3.1

- SONET

- SAS

- XAUI

- 10 and 100 Gb Ethernet

- DisplayPort

- Two sinusoidal interference sources are built into the BSX series BERTScope. These sources are summed internally, and are available as a single differential output on the front panel. When used with the optional external BSXCOMB kit, a variety of sinusoidal interference test configurations are supported, including the CM and DM interference requirements of PCIe Gen3 and Gen4.

#### Amplitude and ISI impairments

For ISI, add externally: for example, long coaxial cable length, or Bessel-Thompson 4th Order Filter with –3 dB point at 0.75 of bit rate, etc.

For applications requiring circuit board dispersion, the BSA12500ISI differential ISI accessory board can be used.

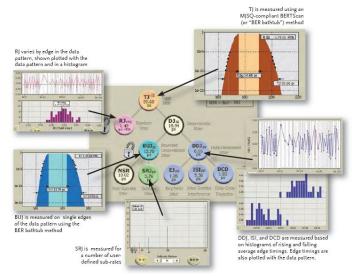

#### **Jitter measurements**

Multi-gigabit serial data channels have eye openings only a couple hundred picoseconds wide – or less. In systems where only a few picoseconds of jitter count, accurate measurement of jitter is essential for managing tight jitter budgets. The BERTScope has two sets of tools which perform these critical measurements.

The Physical Layer Test Suite option includes measurement of Total Jitter (TJ) along with breakdown into Random Jitter (RJ) and Deterministic Jitter (DJ), using the well-accepted Dual Dirac method. The deep, BERT-collected measurements use several orders of magnitude less extrapolation, or in some cases no extrapolation, than oscilloscopes use as a basis for the jitter measurements. This produces inherently more accurate results than measurements made on other instruments which rely on high levels of extrapolation.

MJSQ-compliant Dual Dirac jitter measurement.

The optional Jitter Map is the latest suite of jitter measurements available for the BERTScope. It provides a comprehensive set of subcomponent analysis beyond RJ and DJ, including many measurements compliant with higher data rate standards. Jitter Map can also measure and decompose jitter on extremely long patterns, such as PRBS-31, as well as live data (requires Live Data Analysis option) providing that it can first run on a shorter synchronized data pattern.

Jitter map

Features include:

- DJ breakdown into Bounded Uncorrelated Jitter (BUJ), Data Dependent Jitter (DDJ), Inter-Symbol Interference (ISI), Duty Cycle Distortion (DCD), and Sub-Rate Jitter (SRJ) including F/2 (or F2) Jitter

- BER-based for direct (non-extrapolated) Total Jitter (TJ) measurement to 10<sup>-12</sup> BER and beyond

- Separation of correlated and non-correlated jitter components eliminates mistaking long pattern DDJ for RJ

- Can measure jitter with minimum eye opening

- Additional levels of breakdown not available from other instruments such as: Emphasis Jitter (EJ), Uncorrelated Jitter (UJ), Data Dependent Pulse Width Shrinkage (DDPWS), and Non-ISI

- Intuitive, easy-to-navigate jitter tree

Jitter peak and BER contour measurements made on live data.

# Flexible external jitter interfaces

Flexible external jitter interfaces include the following features:

- Front panel external high frequency jitter input connector jitter from DC to 1.0 GHz up to 0.5 UI (max) can be added, of any type that keeps within amplitude and frequency boundaries

- Rear panel external SJ low frequency jitter input connector jitter from DC to 100 MHz up to 1.1 ns (max) can be added

- Rear panel SJ output

- Sinusoidal interference output front panel connector

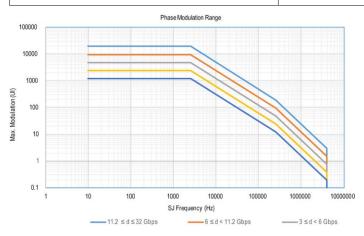

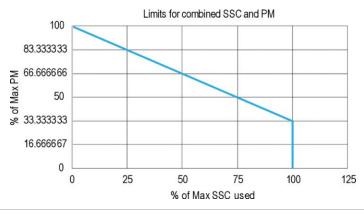

The internal RJ, BUJ, and external high-frequency jitter input is limited to 0.5 UI, combined, further limited to 0.25 UI each when both are enabled. Rear-panel low-frequency jitter input can be used to impose additional jitter; the sum of external low-frequency jitter, internal low-frequency SJ to 10 MHz, PCIe LFRJ and PCIe rSSC (with Option PCISTR) is limited to 1.1 ns. This limit does not apply to Phase Modulation (PM) from Option XSSC.

#### **Jitter impairments**

Bounded uncorrelated jitter:

- Supports data rates from 1.5 to 12.5 Gb/s (BSX125), 24 Gb/s (BSX240), and 32 Gb/s (BSX320)

- Internal PRBS Generator

- Variable up to 0.5 UI

- 100 Mb/s to 2.0 Gb/s

- Band-limited by selected filters

| BUJ rate       | Filter  |

|----------------|---------|

| 100 to 499     | 25 MHz  |

| 500 to 999     | 50 MHz  |

| 1,000 to 1,999 | 100 MHz |

| 2,000          | 200 MHz |

Random jitter:

- Supports data rates from 1.5 to 12.5 Gb/s (BSX125), 24 Gb/s (BSX240), and 32 Gb/s (BSX320)

- Variable up to 0.5 UI

- Band-limited 10 MHz to 1 GHz; 1.5 MHz to 100 MHz in PCle2 mode

- Crest factor of 16 (Gaussian to at least 8 standard deviation or about 1×10<sup>-16</sup> probability)

# Sinusoidal jitter

| Modulation type                                              | Internal SJ<br>frequency | Maximum internal SJ amplitude                                                                      |

|--------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------|

| Phase modulation                                             | 10 Hz to 4 MHz           | Up to 19200 UI ≥11.2 Gb/s                                                                          |

| Low frequency SJ<br>(selectable<br>modulators <sup>1</sup> ) | 1 kHz to 100 MHz         | Up to 1000 ps < 22.4 Gb/s<br>Up to 270 ps <sup>2</sup> 10 - 28.5 Gb/s<br>Up to 130 ps 10 - 32 Gb/s |

| High frequency SJ                                            | 100 MHz to<br>1000 MHz   | 0.5 UI <sup>3</sup>                                                                                |

SJ adjustable from 0 to levels greater than or equal to range in table. Range is decreased at higher modulation rates and/or bit rates. See *Spread spectrum clock and phase modulation* for more PM capability detail and *Sinusoidal Jitter (SJ)* for more SJ capability detail.

# **Testing interface cards**

Finally, a solution to the age-old problem of making physical layer measurements on high-speed line cards, motherboards, and live traffic – the BERTScope Live Data Analysis option. Through novel use of the dual-decision point architecture, the instrument is able to make parametric measurements such as Jitter, BER Contour, and Q-factor in addition to the eye and mask measurements that are usable as standard – all that is required is a clock signal. Add the Jitter Map option to see even more layers of jitter decomposition on live data. No more frustration because the pattern is not known, is unpredictable, or involves rate-matching word insertions. Troubleshooting is so much easier now that the one-button physical layer tests can be employed to provide unique insight.

<sup>3</sup> Total of HFSJ, BUJ, EXT HF jitter and RJ  $\leq$  0.5 UI total

<sup>1</sup> Range is selectable between 1100 ps, 270 ps, and 130 ps maximum; a lower range has lower intrinsic jitter.

<sup>&</sup>lt;sup>2</sup> Full SJ range is 270 ps; with RJ or BUJ the range is reduced to 220 ps.

# **User interfaces**

User interfaces take usability to new heights:

- Easy navigation

- Logical layout and operation

- Multiple ways of moving between screens

- Relevant information right where you need it

- Color coding to alert you to the presence of nonstandard conditions

UI setup screens

The pattern editor, pattern segment editor, and pattern sequencer are contained in a stand-alone view that requires a user supplied VGA-compatible monitor with minimum 1280 x 1024 resolution.

| PatternSequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                          |                                         |                                                                                                                                           |   | ersion: 1.0.61229.0 Tel/tronix                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Ec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | litor 🔻                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                          |                                         |                                                                                                                                           | v | resion: 1.0.61229.0 Tektronix                                                                                                                                            |

| File Edit Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                          |                                         |                                                                                                                                           |   |                                                                                                                                                                          |

| CaptureByLength.ram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\times$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                          |                                         |                                                                                                                                           |   |                                                                                                                                                                          |

| 2 % Imported RA<br>3 ASSIGN WIDTH 3<br>4 %<br>5 0x22cmr300 b0<br>0x45944fal 0x<br>7 0x650s4fal 0x<br>9 0x250s4fal 0x<br>1 0x5344fal 0x<br>1 0x5346fal 0x<br>1 0x<br>1 0x5346fal 0x<br>1 0x<br>1 0x<br>1 0x<br>1 0x<br>1 0x<br>1 0x<br>1 0x<br>1 | 12           re24dadec         0           re345bd2         0           re345b71         0           126def63         0           re44babc3         0           re44babc3         0           re44babc3         0           re44babc3         0           re44babc3         0           re44babc3         0           re45bb3         0           re45bb3         0           re46bb3         0 <tdr> <tdr< th=""><th>x697732af<br/>x422e655f<br/>x85dco2bf<br/>x4D9357f<br/>x97732afe<br/>x32e655fc0<br/>x32afe0<br/>x7732afe0<br/>x7732afe0<br/>x732afe0<br/>x732afe0<br/>x732afe0<br/>x732afe041<br/>x655fc03<br/>x2afe041<br/>x655fc03<br/>x2afe041<br/>x55fc02<br/>x2afe0418<br/>x5ff202c2<br/>xafe04185</th><th>0xe041851e<br/>0xc0830a3c<br/>0x81061479<br/>0x020c2ft2<br/>0x03025145<br/>0x0302512<br/>0x1061479<br/>0x1022ft2<br/>0x10614791<br/>0x106147916<br/>0x022ft2c<br/>0x105145146<br/>0x06147916<br/>0x0514791675<br/>0x852627<br/>0x852645944<br/>0x8522647<br/>0x1455445944</th><th>曼 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵</th><th>0<br/>4<br/>8<br/>12<br/>20<br/>24<br/>28<br/>32<br/>32<br/>32<br/>32<br/>40<br/>44<br/>48<br/>56<br/>60<br/>64<br/>68<br/>72<br/>76<br/>88<br/>88<br/>92<br/>96</th><th>×</th><th>Saving<br/>Save<br/>Save As<br/>Check Syntax<br/>Display Format<br/>Binary Hex<br/>Fill Option<br/>Fill Pattern<br/>Fill Pattern<br/>Truncate<br/>Send To<br/>Generator<br/>Detector</th></tdr<></tdr> | x697732af<br>x422e655f<br>x85dco2bf<br>x4D9357f<br>x97732afe<br>x32e655fc0<br>x32afe0<br>x7732afe0<br>x7732afe0<br>x732afe0<br>x732afe0<br>x732afe0<br>x732afe041<br>x655fc03<br>x2afe041<br>x655fc03<br>x2afe041<br>x55fc02<br>x2afe0418<br>x5ff202c2<br>xafe04185 | 0xe041851e<br>0xc0830a3c<br>0x81061479<br>0x020c2ft2<br>0x03025145<br>0x0302512<br>0x1061479<br>0x1022ft2<br>0x10614791<br>0x106147916<br>0x022ft2c<br>0x105145146<br>0x06147916<br>0x0514791675<br>0x852627<br>0x852645944<br>0x8522647<br>0x1455445944 | 曼 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 贵 | 0<br>4<br>8<br>12<br>20<br>24<br>28<br>32<br>32<br>32<br>32<br>40<br>44<br>48<br>56<br>60<br>64<br>68<br>72<br>76<br>88<br>88<br>92<br>96 | × | Saving<br>Save<br>Save As<br>Check Syntax<br>Display Format<br>Binary Hex<br>Fill Option<br>Fill Pattern<br>Fill Pattern<br>Truncate<br>Send To<br>Generator<br>Detector |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 128 words R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | teady Car                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                          | Find And                                | l Replace                                                                                                                                 |   |                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                        | _                                       | _                                                                                                                                         |   |                                                                                                                                                                          |

| Description T Ty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ре Т                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                          |                                         | _                                                                                                                                         |   |                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                          |                                         |                                                                                                                                           |   |                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                          |                                         |                                                                                                                                           |   |                                                                                                                                                                          |

Pattern and sequence editor

# Physical layer test view