# 32Gbit/s All-in-One Multi-Channel BERT

### MU183020A/MU183021A, MU183040A/MU183041A

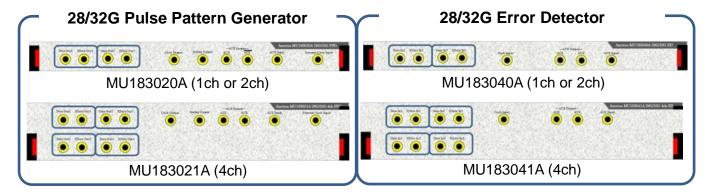

28/32G Multi-Channel PPG and ED Modules

The growing demands of cloud computing and high-resolution video streaming are driving increases in server and storage transmission speed. The transmission capacity of core networks is increasing rapidly to support these demands.

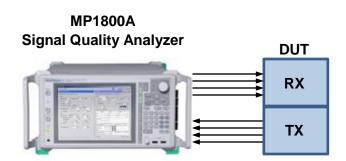

The MP1800A SQA is a modular BERT with built-in Pulse Pattern Generator (PPG), supporting output of high-quality, high-amplitude signals; Error Detector (ED) with high input sensitivity supporting signal analysis, such as Bathtub Jitter and EYE diagram measurements; and Jitter Modulation Source for generating various jitters, including SJ/RJ/BUJ/SSC and supporting jitter tolerance tests.

Installing the 28/32G Multi-Channel PPG and ED modules supports high-speed interconnect up to 32Gbit/s, BER measurements required for device R&D, and simultaneous multi-channel crosstalk tests, as well as more precise and complete signal-integrity analyses.

#### Features

- ✓ Wideband 2.4 to 32.1Gbit/s

- √ 1/2/4ch Selection

- ✓ Simultaneous multi-channel pattern generation and BER analysis

- ✓ Crosstalk testing with individual variable data skew per channel

- ✓ High-input-sensitivity ED

- ✓ High-speed auto measurement (TJ/DJ/RJ/Bathtub Jitter, Eye Diagram)

- √ 32.1Gbit/s Jitter Tolerance testing (with MU181500B, generates RJ/SJ/BUJ/SSC)

- √ 4-tap Emphasis Signal Generator up to 28.1 Gbit/s (with MP1825B)

### Applications

- ✓ CEI-25G, CEI-28G-VSR

- √ 32G Fibre Channel

- ✓ Infiniband EDR (26G)

- √ 100 GbE (25 Gx4), OTU4 (28 Gx4)

- √ 32G DP-QPSK for Long Haul

- ✓ CFP/CFP2, QSFP Module

- ✓ Optical Interconnect

- √ High-Speed Backplanes

MU183020/21A, MU183040/41A does not work together with MU181020A/B and MU181040A/B. Please contact Anritsu for more detailed information and limitations. The specifications and contents of this document may be changed without prior notice.

### **Typical Specifications**

| PPG                | Specification                                                                                      |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Operating Bit Rate | 2.4 to 28.1Gbit/s, 2.4 to 32.1 Gbit/s (Opt-001)                                                    |  |  |  |  |

| Data Output        | Differential, 1/2/4ch (depends on model and option), K-connector, 50ohm                            |  |  |  |  |

| Amplitude          | 500 mV to 2.0 Vp-p / 2 mV Step (Opt-012, 022), 500 mV to 3.5 Vp-p / 2 mV Step (Opt-013, 023)       |  |  |  |  |

| Offset             | -2.0 to +3.3 Voh / 1mV step (Opt-012, 022, 013, 023)                                               |  |  |  |  |

| Cross Point Adjust | 20% to 80%(at amp: 1 to 3.5 Vpp), 30% to 70%(at amp: 0.5 to 0.998Vpp) / 0.1% Step @ 28 or 32Gbit/s |  |  |  |  |

| Data Delay Range   | -1000 m to +1000 mUl / 2mUl step (Opt-030)                                                         |  |  |  |  |

| Tr/Tf              | 12ps (Typical, 20-80%, 28.1Gbit/s, 32.1Gbit/s, Amplitude 3.5Vp-p)                                  |  |  |  |  |

| Jitter             | 8psp-p (Typical, measured with Sampling Scope which has <200fsrms intrinsic jitter)                |  |  |  |  |

| Clock Output       | Single-ended, 1ch, K-connector, 50ohm                                                              |  |  |  |  |

| Frequency          | Full-rate (2.4G to 32.1GHz) or Half-rate (1.2GHz to 16.05GHz) operation                            |  |  |  |  |

| Amplitude          | 0.3 Vp-p min., 1.0 Vp-p max.                                                                       |  |  |  |  |

| Ext Clock Input    | Single-ended, 1ch, SMA-connector, 50ohm                                                            |  |  |  |  |

| Frequency          | 1.2GHz to 16.05GHz                                                                                 |  |  |  |  |

| Amplitude          | 0.3 to 1.0Vp-p (-6.5 to +4.0dBm)                                                                   |  |  |  |  |

| Aux Input          | SMA-connector, 50ohm, Error Injection, Burst Enable                                                |  |  |  |  |

| Aux Output         | SMA-connector, 50ohm Divided Output, Pattern Sync. Output, Burst Out2                              |  |  |  |  |

| Pattern Generation |                                                                                                    |  |  |  |  |

| PRBS               | 2^n-1 (n = 7, 9, 10, 11, 15, 20, 23, 31)                                                           |  |  |  |  |

| Programmable       | 2 to 268,435,456 bits/step 1 bit                                                                   |  |  |  |  |

| Multi-CH operation | Channel Synchronization, Combination                                                               |  |  |  |  |

| ED                   | Specification                                                           |  |  |  |

|----------------------|-------------------------------------------------------------------------|--|--|--|

| Operating Bit Rate   | 2.4 to 28.1 Gbit/s, 2.4 to 32.1 Gbit/s (Opt-001)                        |  |  |  |

| Data Input           | Differential, 1/2/4ch (depends on model and option), K-connector, 50ohm |  |  |  |

| Input Amplitude      | 0.25 to 2.0 Vp-p, Sensitivity 50 mVp-p typ.                             |  |  |  |

| External Clock Input | Single-ended, 1ch, SMA-connector, 50ohm                                 |  |  |  |

| Frequency            | Half-rate operation (1.2GHz to 16.05GHz)                                |  |  |  |

| Amplitude            | 0.3 to 1.0Vp-p (-6.5 to +4.0dBm)                                        |  |  |  |

| Clock Delay Range    | -1000 m to +1000 mUI / 2 m UI step                                      |  |  |  |

| Pattern Detection    |                                                                         |  |  |  |

| PRBS                 | 2 <sup>n</sup> -1 (n = 7, 9, 10, 11, 15, 20, 23, 31)                    |  |  |  |

| Programmable         | 2 to 268,435,456 bits/step 1 bit                                        |  |  |  |

| Aux Output           | SMA-connector, 50ohm, Divided Output, Pattern Sync. Output              |  |  |  |

| Analysis Functions   | Auto Search, Bathtub Jitter, EYE Diagram, EYE Margin, Auto Adjust       |  |  |  |

## **Typical Configuration**

| Model Number  | Model Name               | 28G 1ch           | 28G 2ch + Jitter | 28G 4ch + Jitter | 32G 4ch  |

|---------------|--------------------------|-------------------|------------------|------------------|----------|

|               |                          | High speed device | Interconnect     | CFP2/CFP4        | DP-QPSK  |

| MP1800A       | Signal Quality Analyzer  | V                 | V                | ✓ (x2)           | <b>✓</b> |

| MP1800A-014   | 2-slot for PPG and/or ED | ~                 | V                | ✓ (x2)           | V        |

| MP1800A-032   | 32G PPG/ED Support       | ~                 | V                | ✓ (x2)           | <i>V</i> |

| MU181000A     | 12.5 GHz Synthesizer     | ~                 | V                | V                | <b>V</b> |

| MU181000A-001 | Jitter Modulation        |                   | V                | <b>V</b>         |          |

| MU181500B     | Jitter Modulation Source |                   | V                | V                |          |

| MU183020A     | 28G/32G PPG              | V                 | V                |                  |          |

| MU183020A-001 | 32G Extension            |                   |                  |                  |          |

| MU183020A-012 | 2.0 V Data Out           |                   |                  |                  |          |

| MU183020A-013 | 3.5 V Data Out           | ~                 |                  |                  |          |

| MU183020A-030 | 1ch Data Delay           |                   |                  |                  |          |

| MU183020A-022 | 2ch 2.0 V Data out       |                   | V                |                  |          |

| MU183020A-023 | 2ch 3.5 V Data out       |                   |                  |                  |          |

| MU183020A-031 | 2ch Data Delay           |                   | <b>V</b>         |                  |          |

| MU183021A     | 28G/32G x 4ch PPG        |                   |                  | V                | <b>V</b> |

| MU183021A-001 | 32G Extension            |                   |                  |                  | <b>✓</b> |

| MU183021A-012 | 4ch 2.0 V Data Out       |                   |                  | <b>'</b>         |          |

| MU183021A-013 | 4ch 3.5 V Data Out       |                   |                  |                  | <b>✓</b> |

| MU183021A-030 | 4ch Data Delay           |                   |                  | V                | <b>V</b> |

| MU183040A     | 28G/32G ED               | V                 | V                |                  |          |

| MU183040A-001 | 32G Extension            |                   |                  |                  |          |

| MU183040A-010 | 1ch ED                   | ~                 |                  |                  |          |

| MU183040A-020 | 2ch ED                   |                   | V                |                  |          |

| MU183041A     | 28G/32G x 4ch ED         |                   |                  | V                |          |

| MU183041A-001 | 32G Extension            |                   |                  |                  |          |

**ANRITSU CORPORATION**

5-1-1 Onna, Atsugi-shi, Kanagawa, 243-8555

Phone: +81 46 223-1111 Printed in Japan 2011-11 MG